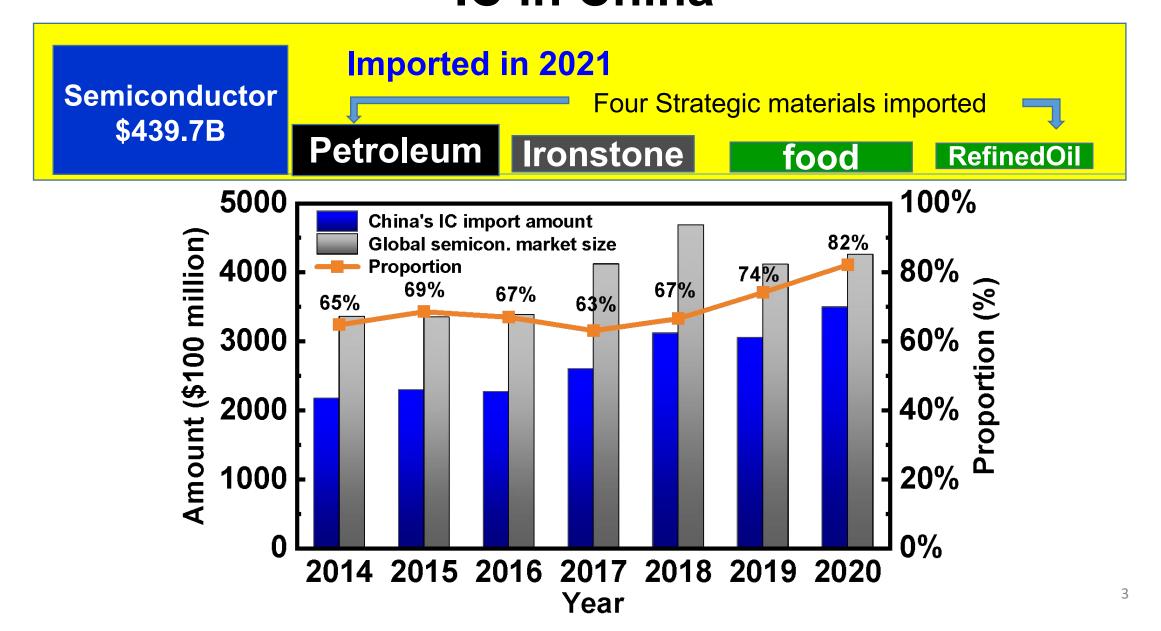

# New Approach of Chip Manufacturing in China

### **Prof. Hanming Wu**

Academician of the Chinese Academy of Engineering School of Micro-Nano Electronics, Dean Zhejiang University, PRC

## Highlight

- 1. Background

- 2. China Future approach

- 3. Summary

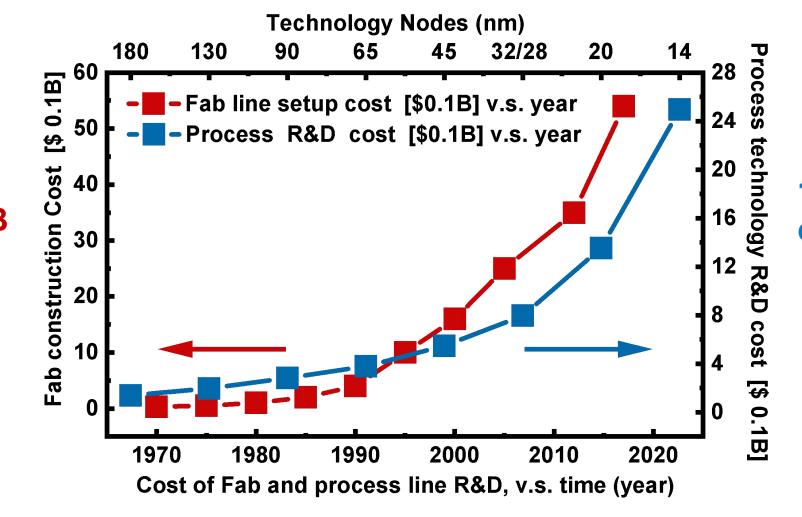

## Cost of Advaced Technology Nodes Fab & R&D

14 nm Fab cost US\$ 6B

14 nm R&D cost US\$ 2B

## **Background**

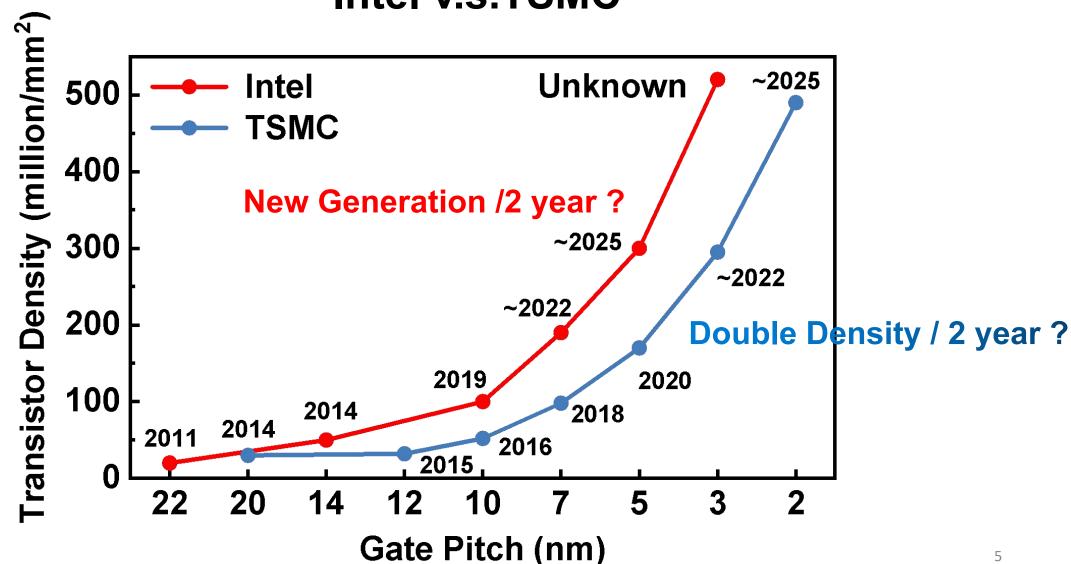

#### Intel v.s.TSMC

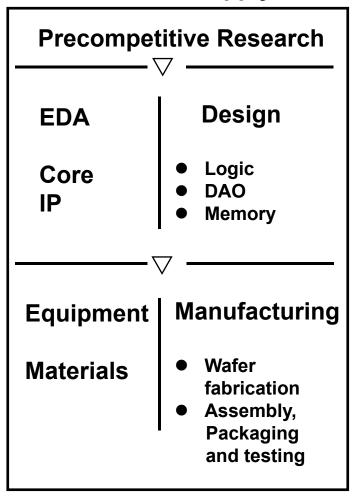

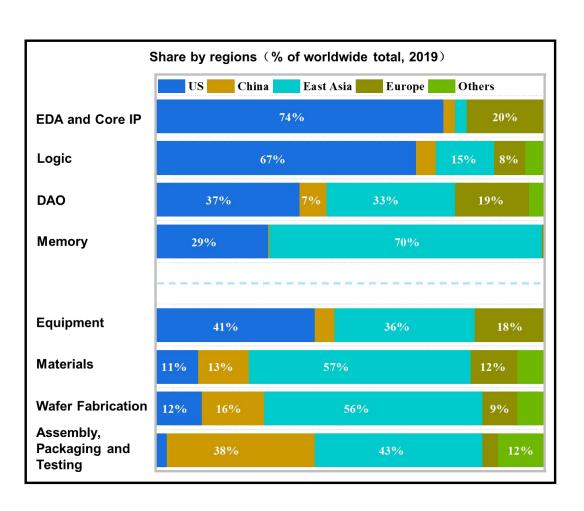

## The Global Semiconductor Supply Chain Based On Geographic Specialization Has Delivered Enormous Value For The Industry

#### **Semiconductor Supply Chain**

Cost savings vs.

Fully localized

"self-sufficient"

Supply chains:

\$0.9-1.2 T

Avoided upfront Investment

\$45-125 B

Annual cost efficiencies

35-65%

Enabled reduction in semiconductor prices

## **Worldwide Evolution of CMOS Nodes**

| CMOS Node                                                            | 65nm                           | 45nm<br>HkMG                | 32nm<br>(2009)                 | 22nm<br>Tri-Gate<br>(2011)          | 14 nm<br>FinFET<br>( <i>IEDM</i> '14)                             | 10nm<br>(FinFET<br>IEDM '17)                                          |

|----------------------------------------------------------------------|--------------------------------|-----------------------------|--------------------------------|-------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|

| $L_g$ (nm)                                                           | 35                             | 35                          | 30                             | 26                                  | 22                                                                | <u>20</u>                                                             |

| Contacted Poly Gate/(Metal 0) Pitch (nm)                             | 220                            | 160<br>0.703                | 112.5<br>0.711                 | 90                                  | 70<br>(56)                                                        | <u>54</u><br>(36)                                                     |

| SRAM Area<br>(mm²)                                                   | 0.57                           | 0.346                       | 0.148                          | 0.092                               | 0.0588                                                            | 0.0312                                                                |

| n/p-MOS $I_{on}$<br>mA/mm @<br>$V_{dd}$ =1V &<br>$I_{off}$ =100nA/mm | 1.21/<br>0.71<br><b>leng</b> f | 1.36/<br>1.07<br>th scaling | 1.55/<br>1.21<br><b>factor</b> | 1.07/0.85<br>V <sub>dd</sub> =0.75V | 1.04/1.04<br>V <sub>dd</sub> =0.7V<br>(I <sub>off</sub> =10nA/mm) | 1.8/1.5<br>V <sub>dd</sub> =<br>0.7v<br>I <sub>off</sub> =10nA<br>/mm |

## **Background**

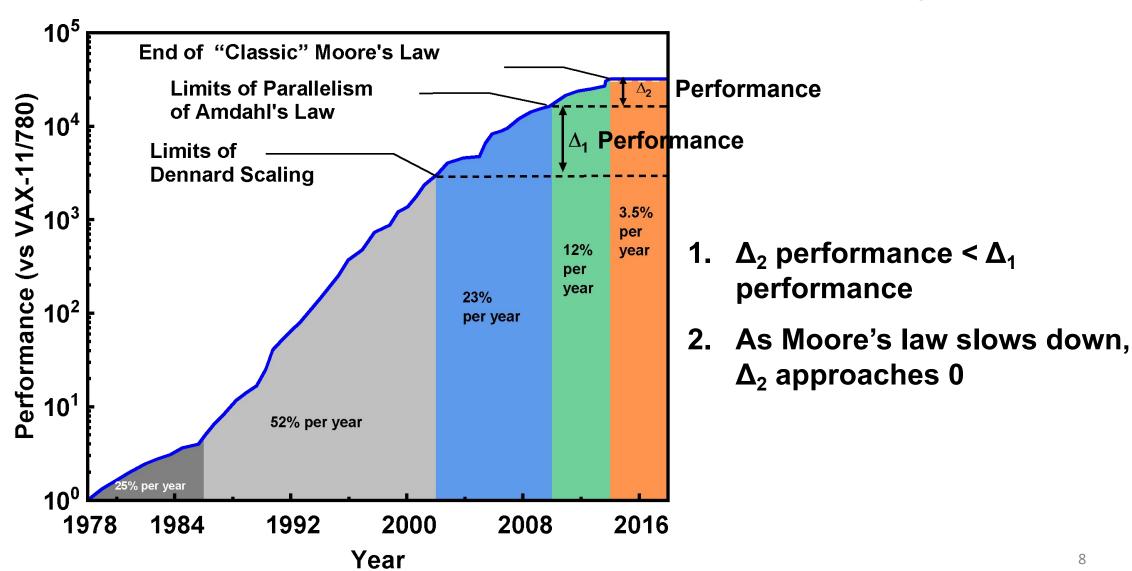

#### Slow Down Moore's Law Provide an Opportunity

## Highlight

- 1. Background

- 2. China Future approach

- 3. Summary

## Manuefacturing Technology in China Mainland

- 1. 28/14nm manufacturing processes for some special products is ready

- 2. 300mm wafer start to provide to chip manufacturing fab

- 3. Some key process equipments, such as advaced plasma etch tools, are technically ready to support chip manufactruing

- 4. Specialized CPU and 5G chips can be made in local chip Feb.

From: https://www.163.com/dy/article/HHE8F40E055225XN.html

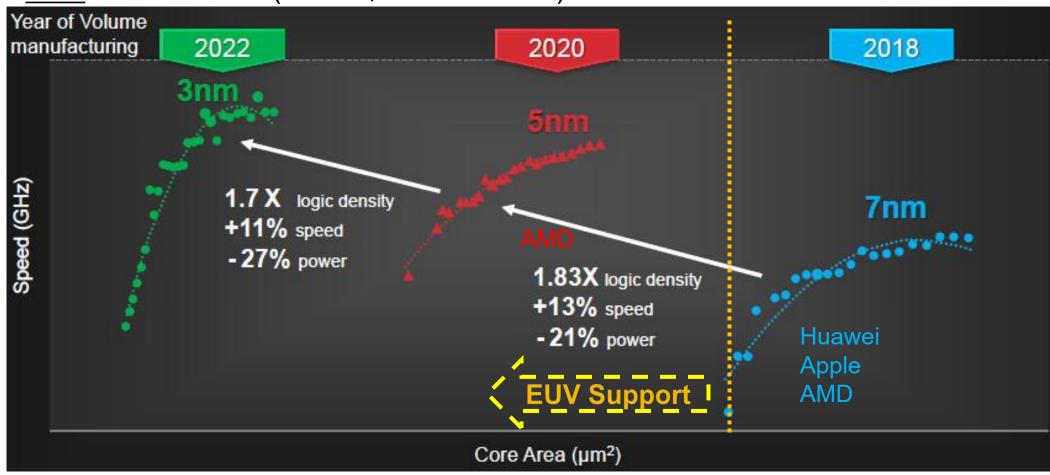

### **TSMC Technology Roadmap**

• Fine Feature size (TSMC, ISSCC 2021)

## **Technology Trends for Future Applications (Quadrant)**

#### Si Technology

VN+Si

Von Neumann **Paradigm**

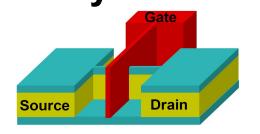

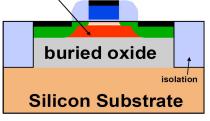

**Planar** MOSFET

3D FET: FinFET.

Nanowire FET Nanosheet FET

Bottleneck:  $P \propto f^3$

VN-+Si

**Brain-Like Technology**

High-efficiency low-power solutions:

Neurons networks

In-memory computing

**Artificial Intelligence** Industrialization

Architecture **Emerging**

Von Neumann (VN) Architecture

Quasi-Logic **Technology**

VN Architecture with

**Novel Devices**: NCFET **PCFET**

SET

other non-CMOS devices

**Beyond CMOS** Technology

#### **Emerging Technology**

**New-logic Devices:**

Spintronic device Ouantum device

Non-VN Architecture:

Quantum computing Neuromorphic computing

**Early Stage Exploration**

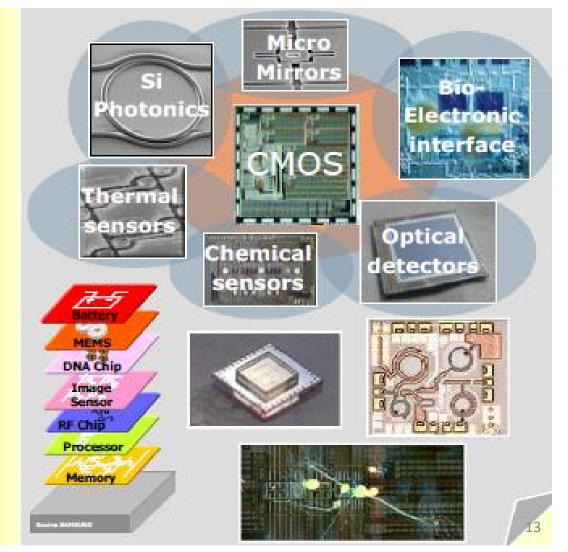

## **Two Major Technology Approaches**

From IMEC

**More Moore**

**More than Moore**

## Post-Moore's Technology Trend

#### **Market Driven**

- HiSpd Computing

- Mobile Computing

- Autonomous perception& Calculation (IoT)

## **Technology**

- Logic technologies

- Ground rule scaling

- Performance boosters

- Performance-power-area (PPA) scaling

- 3D integration

- Memory technologies

- DRAM technologies

- Flash technologies

- Emerging non-volatile-memory (NVM) technologies

# PPAC Next Target in 2~3 years

- (P) Performance: Frequency raise 15%@ Voltage

- (P) Power: Reduce>30%@Same performance

- (A) Area: Reduce 30%chip area;

- (C) Cost: Wafer raise < 30% -Unit cost reduce 15%

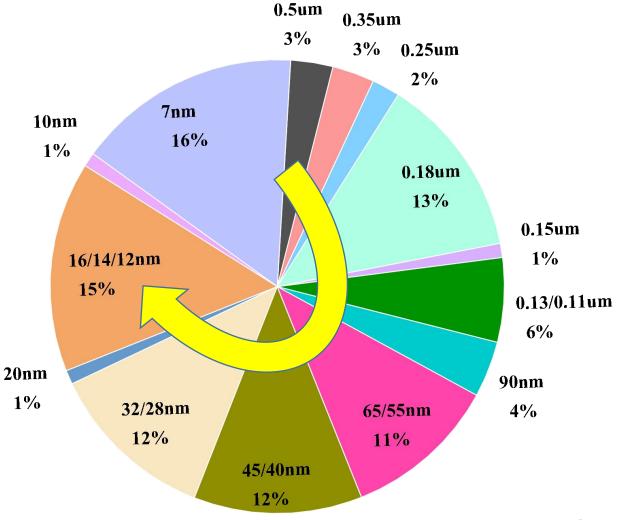

## Large Market Share in Matured Technology

- 83% market share at nodes above 10 nm

- Great room for innovation

**From Industrial Securities**

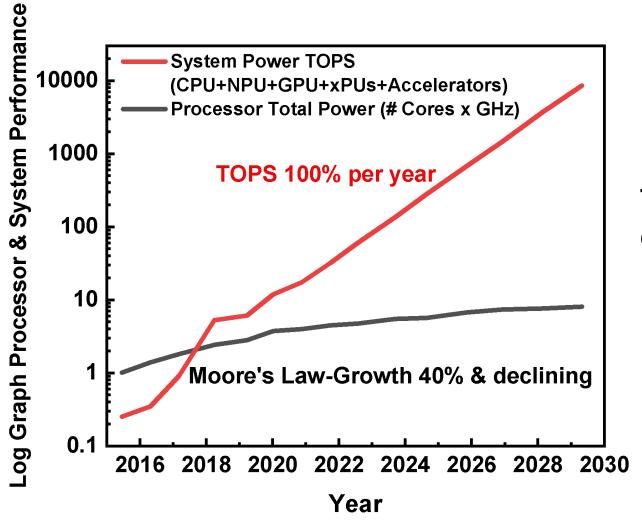

# IC Technology Advancement Cannot Support The Increasing Demand in Computing Capability

How to meet the huge demands of computing capacity?

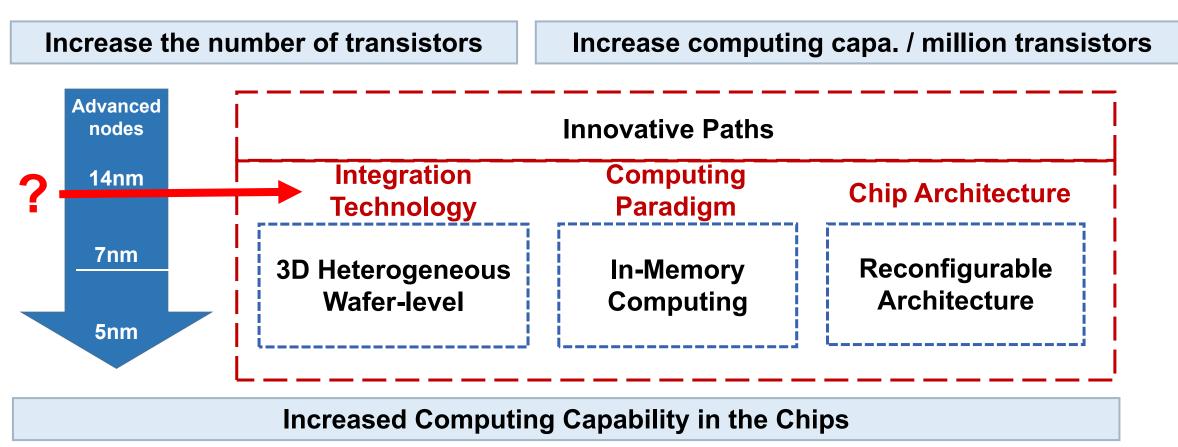

## Future Trends for High Computing Capability Innovations

High computing capability can be achieved by innovations on computing paradigm, chip architecture, and integration technology

Computing Capability (CC) ~ transistor number (millions) × CC/million transistors

## **Future Trends for High Computing Capability Innovations**

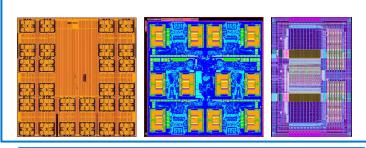

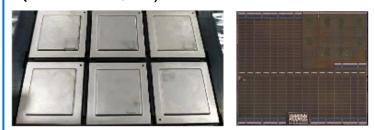

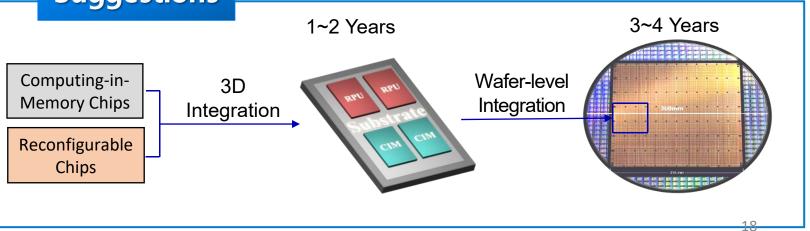

## **Computing-in-memory Chips**

64 MB (world's largest) computingin-memory chip featuring 28 nm technology node and 300-500 TOPS

Reconfigurable Chips

Mixed-grain reconfigurable processing unit featuring 40 nm technology node and the world-leading energy efficiency (~20TOPS/W)

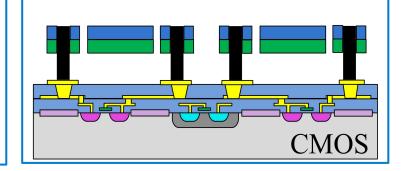

3D Integration Technology

TSV-based 3D heterogeneous integration has been demonstrated

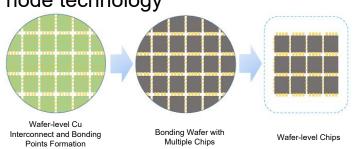

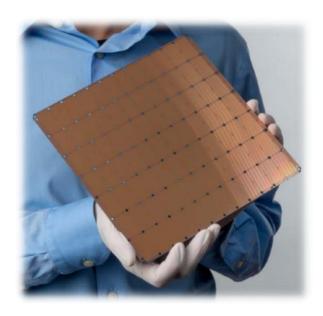

#### **Wafer-level Integration**

Multiple patterning technology for interconnect fabrication with large node technology

#### **Suggestions**

Tsinghua Uni. Prof. Huaqiang Wu

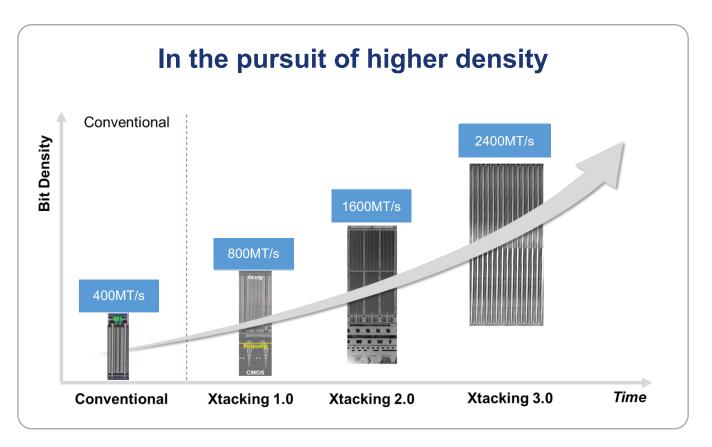

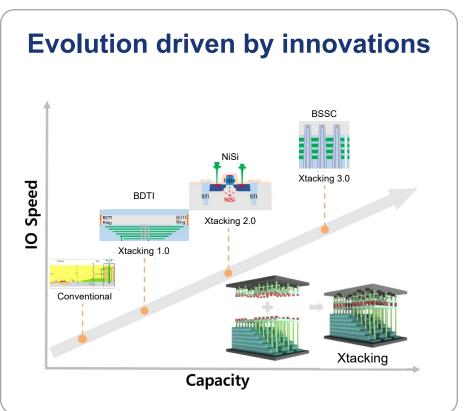

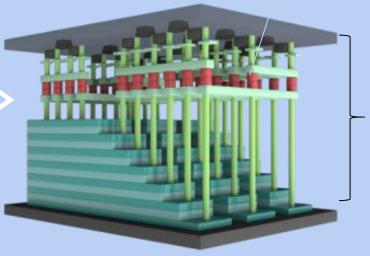

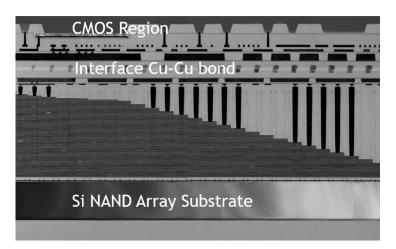

## **Xtacking: From Revolution to Evolution:**

To achieve higher density, higher speed and fast TTM, new innovations has been introduced to address the challenges along with the vertical scaling.

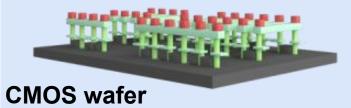

### **Xtacking™ Concept**

Independent processing

On separated wafers

Memory cell wafer

Xtacking™ architecture

Wafer bonding processing with millions of metal **VIAs**

(Vertical Interconnect Accesses)

Into one wafer

**FMS 2018**

**Higher IO speed**

Up to 3.0Gbps IO speed

**Higher bit density**

CMOS Array hybrid bonding enhances Array Efficiency

**Faster time-to-market**

Modularized, parallel approach to product development and manufacturing

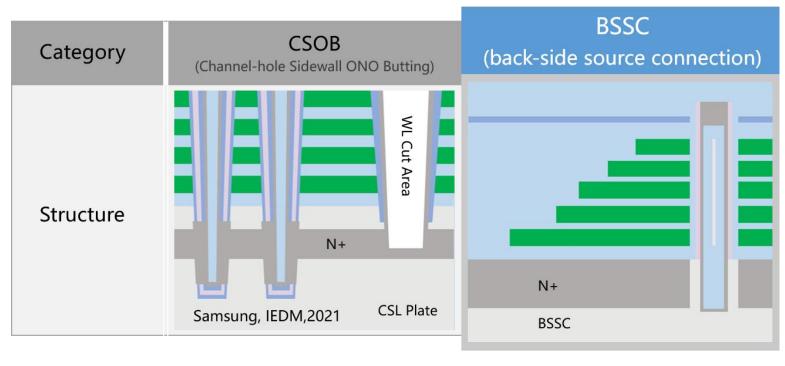

- BSSC (Back Side Source Connect) in Xtacking®: Simple process, lower cost and much lower defect level

- Transition from front side deep trench process to back side surface process much faster yield learning curve

**FMS 2022**

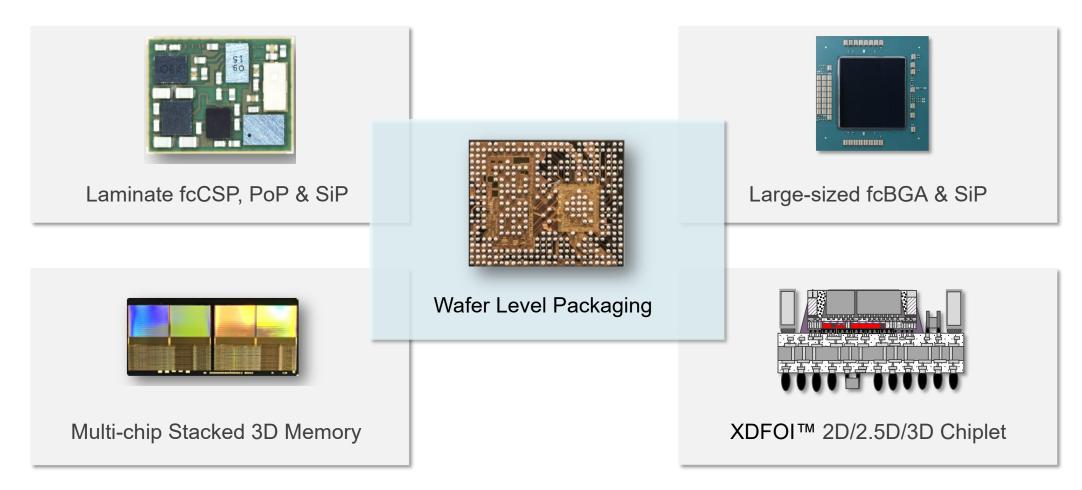

### **JCET Group Technology Portfolio**

- > Comprehensive R&D and mass production experiences in conventional and advanced packaging

- > JCET Group's technologies and services have been recognized by the world's leading customers

### **JCET Group Technology Development Directions**

Accelerate the R&D and MP of high-performance technologies incl. 2.5D and 3D

Enhance technical valueadded services such as highend testing and design services

Technology development for new markets incl. automotive, high-performance storage & computing

Promote the implementation of intelligent manufacturing

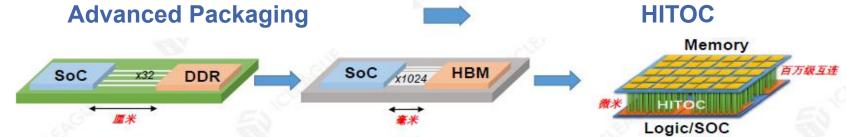

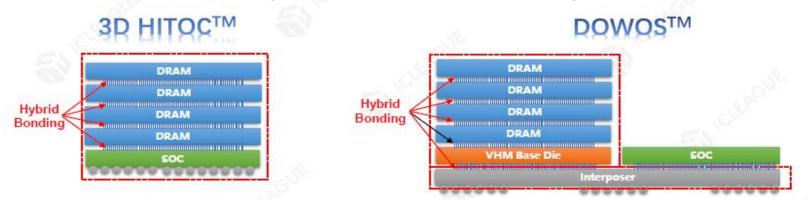

## Heterogeneous Integration Technology On Chip (HITOC)

#### **Traditional Achitecture**

Chips from Corporation C\*: 18 GB, one wafer (46,225 mm<sup>2</sup>) 16 nm Technology Node

#### **HITOC**

Chip from ICLEAGUE: 19.8 GB, one die (800 mm²) 40 nm Technology Node Scalable on Demand

## Heterogeneous Integration Technology On Chip (HITOC)

HITOC exhibits advantages in performance, power consumption, area, bandwidth, latency, and fabrication simplicity etc.

#### **CSTIC 2022:**

- Nano Lab and ICLEAGUE co-invented the large-capacity 3D memory-integrated chip "Cuckoo"

- 800mm² area, Heterogeneous multi core processor, Intgelligent-NOC, Distributed SRAM, High bandwidth low latency 3D DRAM, 6 GB capacity, 6TB/s memory bandwidth

# The Success of Technology Transformations Based on Integration of Industry & Education

HK/MG

**Strained Si**

Raised S/D

**Berkeley → Intel**

- Gate dielectric and thickness

- Increase Leakage current

- Reduce reliability

- High k gate dielectric

Yale → Ti

Strained Si, Ge, SiGe

MIT → Intel

- SCE & Series resistance

- Contact resistance

- Ultra shallow junction technology

- Raised S/D, Schottky S/D, etc

$IBM \rightarrow IBM$

It takes more than ten years to transfer the achievement to industry

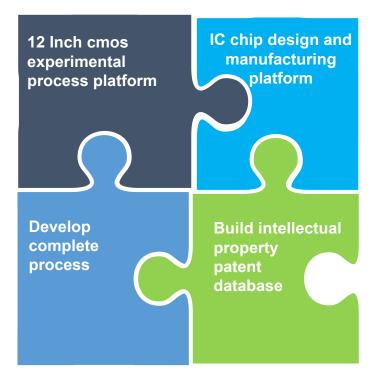

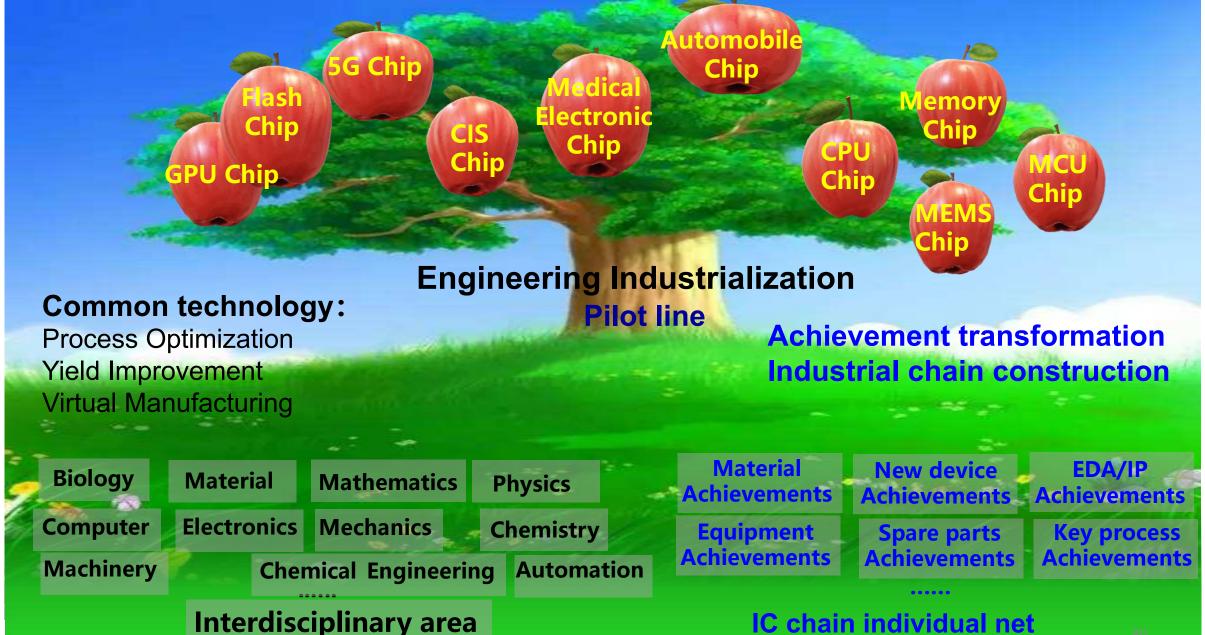

#### Three Major Functions of The Platform with a Complete Process Flow

#### **Co-innovation**

## **Design-manufacture** combination platform

- ✓ 55 nm 12 inch process line

- ✓ For the post moore fragmentation Market

### **Talent training**

Reconstruction of engineering college with combo of industry & Edu

- ✓ New engineering: training of excellent engineers

- ✓ Integration between industry and education

#### **Ecosystem**

#### IC chain construction

- ✓ Complete process verification for equipment and material

- ✓ Incubate innovative enterprises

## R&D Mini Line With Complete Process Flow at ZJU

July 2021,Roof-sealing The end of 2021,Main body completion April 2022,Tape-out September 2022,Wafer out

## **R&D Mini Line With Complete Process Flow at ZJU**

April 2022 all tools moved in

#### Full Process Flow Pilot Platform For Interdisciplinary Transformation To Industrialization

IC chain individual net

## Highlight

- 1. Background

- 2. China Future approach

- 3. Summary

## **Summary**

- Advanced process technology development is extremely challenging due to some antiglobalization, China technology roadmap has to be refocused to More than Moore path.

- More than Moore is one of the most promising technology, such as new structure, advanced package, specialized process technology

- China IC market capacity is huge in the post-Moore era for matured process technology nodes, due to diversified IC products on China market

- Education for Chip students would be engineering oriented instead of pure theoretic subject

- Globalization is the best way to develope IC technology. There would be NO WINNER if anti-globalization becomes reality

- Localized industry supply chain needs to be enhanced to secure IC industry in China, especially in epidemic peroid

# Thank You!

Https: http://hic.zju.edu.cn/